# COMPUTER-AIDED-DESIGN METHODS FOR EMERGING QUANTUM COMPUTING TECHNOLOGIES

| Approved by:                                             |

|----------------------------------------------------------|

| Dr. Mitchell A. Thornton (Chair & Dissertation Director) |

| Dr. Hesham El-Rewini                                     |

| Dr. Fatih Kocan                                          |

| Dr. D. Michael Miller (Univ. of Victoria, BC, Canada)    |

| Dr. Sukumaran Nair                                       |

| Dr. Stephen A. Szygenda                                  |

# COMPUTER-AIDED-DESIGN METHODS FOR EMERGING QUANTUM COMPUTING TECHNOLOGIES

A Dissertation Presented to Graduate Faculty of the

School of Engineering

Southern Methodist University

in

Partial Fulfillment of the Requirements

for the degree of

Doctor of Philosophy

with a

Major in Computer Engineering

By

David Dov Yehuda Feinstein

(B.S.E.E., Technion-Israel Institute of Technology, 1977) (M.S.E.C.E., University of Houston, 1992)

May 17, 2008

## © COPYRIGHT 2008

## David Dov Yehuda Feinstein

All Rights Reserved

#### **ACKNOWLEDGEMENTS**

I was very fortunate to have Prof. Thornton as my teacher, advisor and mentor. His superb classes on verification and CAD methods quickly brought me to the frontier of digital logic research. Prof. Thornton has the unique requirement that his graduate class projects must be submitted in the form of conference papers. This required me to write six practice conference papers during his classes, an experience that turns out to be invaluable for the success of my research. Prof. Thornton inspired me to publish quality work extensively with great care for details. He encouraged me to attend many international and national conferences, during which I met his many and diverse collaborators, all in the forefront of digital logic research. Coming from a similar background in the computer industry, Prof. Thornton was very supportive in my efforts to achieve excellence in studies and research while still running my high tech company.

It was a great honor to work with and to learn so much from Prof. D. Michael Miller while producing many of the papers at the core of this dissertation. A long time collaborator of Prof. Thornton, Prof. Miller graciously agreed to serve in my committee.

Many thanks to Prof. El-Rewini, Prof. Szygenda, Prof. Nair and Prof. Kocan for their time, support, valuable comments, and enthusiasm to serve in my committee. I benefited immensely from taking their graduate classes at SMU.

To accomplish a Ph.D. in computer engineering at the age of 53 while running a high tech company like INNOVENTIONS Inc required tremendous support from all my dedicated employees. Special thanks go to my secretary Monika Frausto for grammatically reviewing all my research work. Scott LaRoche and Jose Nunez had to work much harder to cover for the extra time I spent on this research.

The support of my family and many friends was crucial throughout the four years of my PhD "adventure". My wife Orna patiently waited for me to come home at 9:00 pm every day, knowing that I may still spend several more hours of study at home. With her love and support I was better able to succeed in this research. My son Oren and my daughter Donna were great fans of my work and encouraged me to reach the tough finish line. Oren's achievement in obtaining a B.S.E.E. from UT Austin with 4.0 GPA challenged me to accomplish the same with my graduate classes at SMU. My late father, Benjamin Feinstein, encouraged me to be an intellectual and he instilled in me the love of books in early childhood.

I am blessed with many supportive friends. Prof. Çetin Koç, my mentor during my MSEE studies, was instrumental in my choice of SMU. Prof. Nachum Dafny was a great inspiration on the importance of getting a PhD. Ron Avni, Menachem Zucker, David Prusman, Avi Alon, Shay Korentayer, Yadin David, Isaac Peretz, and Moti and Ora Tenenhaus followed my progress with much enthusiasm. Last but not least, I would like to thank my life time friend, Avery More, for his great support and encouragement.

Feinstein, David Dov Yehuda

B.S.E.E., Technion - IIT, 1977 M.S.E.C.E., University of Houston, 1992

Computer Aided Design Methods for **Emerging Quantum Computing** Technologies

Advisor: Professor Mitchell A. Thornton

Doctor of Philosophy conferred May 17, 2008

Dissertation completed April 18, 2008

Emerging quantum computing technologies are poised to replace standard CMOS logic when the exponential size reduction reaches sub-atomic dimensions. Quantum circuits are reversible and therefore promise the potential of computation without energy loss. This research considers computer aided design (CAD) methods for all major aspects of quantum computing circuit design including logic synthesis, simulation, verification, and testing.

The technologies we investigate include quantum cell automata (QCA) and general quantum circuits (QC), with significantly more emphasis on the later. The recently introduced quantum multi-valued decision diagram (QMDD) provides an efficient method to represent and simulate quantum (and other classical reversible) circuits. A major contribution of this dissertation is the development of a sift-like minimization as well as structure metrics based minimization techniques for QMDD. We have used the enhanced QMDD to efficiently simulate quantum circuits as well as quantum vectors.

vi

Our early investigation of reversible logic is concerned with a virtual implementation that uses a direct translation of relatively complex binary functions into circuits composed of Fredkin reversible gates. This allowed us to project size and speed complexity of complex reversible circuits, although this direct translation approach fails to minimize garbage inputs and outputs. To achieve proper garbage minimization, one must synthesize reversible logic using gate cascades with appropriate optimization methods embedded that attempt to minimize the total number of lines in the circuit. To that end, we developed a novel QMDD-based tool for cascade logic synthesis that utilizes the QMDD minimized variable order for lexicographical synthesis with garbage minimization included as an optimization criterion.

We developed a synthesis tool that investigates the QCA native 3-input majority gates ability to implement complex logic circuits. In particular, we explore the benefit of transforming the logic description into *exclusive sum of products* (ESOP) forms prior to implementation in the majority gates.

We survey recent efforts in establishing the foundation for QC testing and fault tolerant QC. We project the potential use of random tests as well as *built in self test* (BIST) techniques for future QC. A major contribution of this dissertation is the investigation of partially redundant reversible logic. Detection of partially redundant logic within any design, reversible or irreversible, has ramifications for logic synthesis, for design verification, and for *design for test* (DFT) issues.

## TABLE OF CONTENTS

| LIST OF FIGURES                                                   | xiii |

|-------------------------------------------------------------------|------|

| LIST OF TABLES                                                    | xvi  |

| Chapter                                                           |      |

| 1. INTRODUCTION                                                   | 1    |

| 1.1. Emerging Quantum Computing Technologies                      | 3    |

| 1.2. Quantum Computing Computer Aided Design Tools                | 7    |

| 1.3. Impact and Contributions of this Research                    | 9    |

| 1.4. Organization                                                 | 10   |

| 2. FROM QUANTUM MECHANICS TO QUANTUM COMPUTING                    | 13   |

| 2.1. Key Ideas of Quantum Mechanics                               | 13   |

| 2.1.1. Linear Algebra Preliminaries                               | 14   |

| 2.1.2. The Stern-Gerlach Experiment and the Idea of Superposition | 17   |

| 2.1.4. Entanglement                                               | 20   |

| 2.1.5. Measurement and Decoherence in Quantum Mechanics           | 21   |

| 2.2. Reversible Logic                                             | 25   |

| 2.2.1. Defining Reversible Logic                                  | 25   |

| 2.2.2. Symmetry in Reversible Logic                               | 27   |

| 2.2.3. Reversible Gates Cascade                                   | 28   |

| 2.2.4. Logic Function Realization with Classical Reversible Gates | 30   |

| 2.3. Quantum Computation and Quantum Information                  | 32   |

| 2.3.1. Quantum Computing Algorithms                               | 32   |

| 2.3.2. Quantum Bits and Registers                           | 34   |

|-------------------------------------------------------------|------|

| 2.3.3. Quantum Operations on a Single Qubit                 | 35   |

| 2.3.4. Elementary Quantum Gates and Quantum Circuits        | 36   |

| 2.3.5. The Walsh-Hadamard Transformation                    | 39   |

| 2.3.6. The Beck-Zeilinger-Bernstein-Bertani Theorem         | 40   |

| 2.3.7. Decoherence and Fault Tolerance for Quantum Circuits | s 43 |

| 2.4. Quantum Cellular Array Fundamentals                    | 44   |

| 2.4.1. The Quantum Cellular Array Basic Cell and Wires      | 45   |

| 2.4.2. The Native Gates of QCA                              | 46   |

| B. REPRESENTATION AND SIMULATION OF QC                      | 48   |

| 3.1. Quantum Simulation on Classical Computers              | 48   |

| 3.1.1. Classical Binary Decision Diagrams (BDD)             | 49   |

| 3.1.2. Early Quantum Circuit Simulation Tool Using BDDs     | 50   |

| 3.1.3. The QuIDDPro Tool                                    | 50   |

| 3.1.4. The Binary Control Signal Constraint                 | 50   |

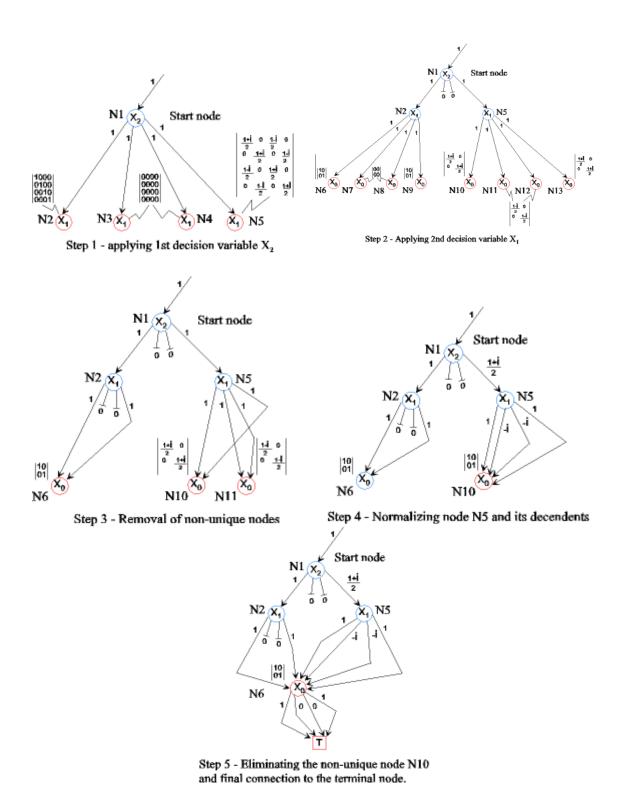

| 3.2. The QMDD Data Structure                                | 51   |

| 3.2.1. Properties of the QMDD                               | 52   |

| 3.2.2. QMDD Representation is Canonic                       | 54   |

| 3.2.3. A QMDD Example                                       | 55   |

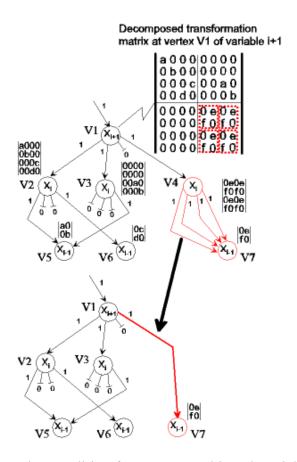

| 3.2.4. QMDD Construction and Matrix Operations              | 59   |

| 3.3. QMDD Sift-Like Minimization and Manipulation           | 59   |

| 3.3.1. Dynamic Variables Re-ordering Using Sifting          | 60   |

|    | 3.3.2. QMDDs without Skipped Variables                                   | 62     |

|----|--------------------------------------------------------------------------|--------|

|    | 3.3.3. Skipped QMDD Variables Appear in QC Cascades                      | 65     |

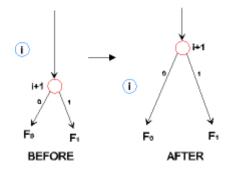

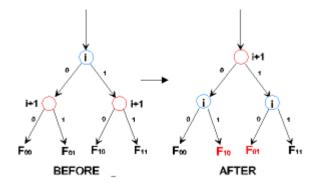

|    | 3.3.4. Local Variable Swap for QMDD with no Skipped Variables            | 72     |

|    | 3.3.5. The QMDD Sifting Procedure                                        | 75     |

|    | 3.3.6. QMDD Minimization Results with Sifting                            | 76     |

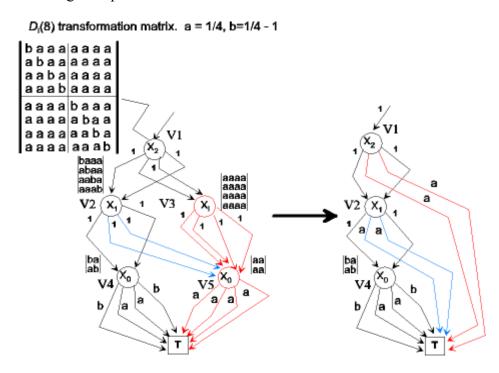

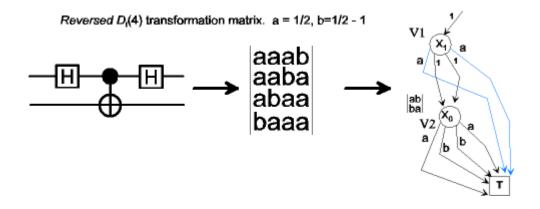

|    | 3.4. Data Structure Metrics of Quantum Multiple-valued Decision Diagrams | 77     |

|    | 3.4.1. Exploring QMDD Data Structure Metrics                             | 79     |

|    | 3.4.2. Improving QMDD Minimization with the Data Structure Metrics       | 84     |

|    | 3.4.3. Experimental Improvements with the Data Structure Metrics         | 86     |

|    | 3.5. Using QMDD for QC Simulation.                                       | 89     |

| 4. | SYNTHESIS OF QUANTUM AND CLASSICAL REVERSIBLE CIRCUITS                   | S . 92 |

|    | 4.1. ESOP Techniques for Majority Gate Based Logic Synthesis for QCA     | 92     |

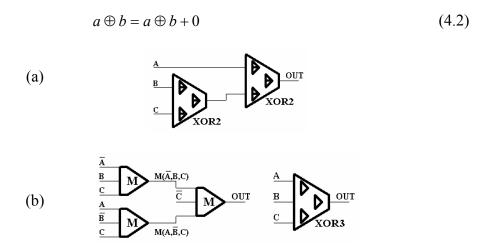

|    | 4.1.1. Multi-input XOR and AND/OR Implementation in QCA                  | 93     |

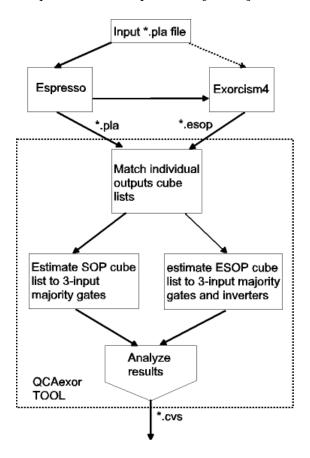

|    | 4.1.2. The QCAexor Tool                                                  | 97     |

|    | 4.1.3. Experimental Results in ESOP vs. SOP QCA Synthesis                | 98     |

|    | 4.2. Virtual Implementation of Reversible Logic using Direct Translation | . 101  |

|    | 4.3. Survey of Synthesis Methods for Reversible Gate Cascades            | . 105  |

|    | 4.3.1. Exhaustive Approaches for Synthesis                               | . 106  |

|    | 4.3.2. Synthesis Using Formal Verification Methods                       | . 107  |

|    | 4.3.3. Template Based Synthesis                                          | . 107  |

|    | 4.3.4. Lexicographic Based Reversible Logic Synthesis                    | . 109  |

|    | 4.3.5. Group Theory and Symmetry Based Synthesis                         | 111    |

|    | 4.3.6. Spectral and Reed-Muller Transformation Techniques            | 112 |

|----|----------------------------------------------------------------------|-----|

|    | 4.3.7. Synthesis Approaches Based on Decision Diagrams               | 114 |

|    | 4.4. Using QMDD Minimization for Efficient Synthesis                 | 114 |

|    | 4.4.1. Circuit Complexity versus QMDD Metrics                        | 115 |

|    | 4.4.2. Lexicographic Synthesis Approach                              | 121 |

|    | 4.4.3. The QMDDsyn Framework Synthesis Results                       | 124 |

| 5. | TESTING AND VERIFICATION OF QUANTUM CIRCUITS                         | 128 |

|    | 5.1. Testing of Reversible Logic                                     | 128 |

|    | 5.2. Towards a Unified QC Fault Model                                | 130 |

|    | 5.3. Technology Specific Defect Characterization for QCA Testing     | 133 |

|    | 5.4. Partially Redundant Reversible and Irreversible Logic Detection | 134 |

|    | 5.4.1. Partially Redundant Logic in Irreversible Logic               | 135 |

|    | 5.4.2. Partially Redundant Logic in Reversible Logic                 | 136 |

|    | 5.4.3. Circuit Modification Strategy                                 | 137 |

|    | 5.4.4. Gate Modification for Irreversible Logic                      | 138 |

|    | 5.4.5. Gate Replacement for Reversible Logic                         | 139 |

|    | 5.4.6. Irreversible Benchmark Circuits Results                       | 141 |

|    | 5.4.7. Reversible Logic Benchmark Circuits Results                   | 143 |

|    | 5.4.8. Results with Randomly Generated Reversible Circuits           | 144 |

| 6. | CONCLUSION AND FUTURE RESEARCH                                       | 147 |

|    | 6.1. Conclusions and Main Contributions                              | 147 |

|    | 6.2. Areas of Future Research                                        | 149 |

|           | 6.2.1 Limitations of Quantum Circuit Simulation on Classical Computers | 149 |

|-----------|------------------------------------------------------------------------|-----|

|           | 6.2.2 Other Quantum Circuit Simulators                                 | 150 |

|           | 6.2.3 Direct Synthesis of Quantum Circuits from QMDD                   | 150 |

|           | 6.2.4 Testing of Quantum Circuits                                      | 151 |

| Reference | ces                                                                    | 152 |

# LIST OF FIGURES

|    | •   |     |

|----|-----|-----|

| _  | 101 | 110 |

| П, | וצו | ш   |

| _  |     |     |

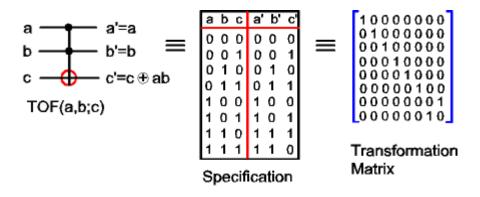

| 1.1. Transformation Matrix Representation of the Toffoli Gate | <i>6</i> |

|---------------------------------------------------------------|----------|

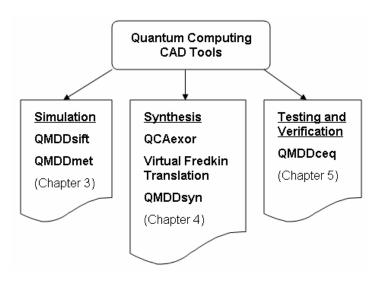

| 1.2. Overview of the Quantum Computing CAD Tools              | 7        |

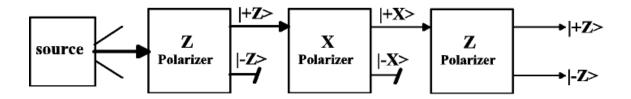

| 2.1. The Stern-Gerlach Experiment                             | 17       |

| 2.2. n-variable Toffoli Gate                                  | 27       |

| 2.3. Toffoli Gate as a cycle(6,7) Operation                   | 28       |

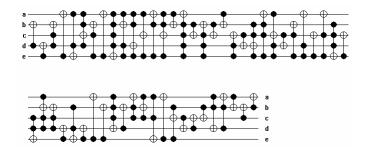

| 2.4. The 5-variable "hwb5" Cascade of Gates                   | 29       |

| 2.5. A Cascade of 4 Gates with 4 Variables                    | 30       |

| 2.6. Logic Functions by Toffoli and Fredkin Gates             | 31       |

| 2.7. The General Controlled Operation                         | 36       |

| 2.8. The Deutsch-Toffoli Universal Gate                       | 37       |

| 2.9. Basic QCA Cell (a) and (b) QCA Wires                     | 45       |

| 2.10. QCA 3-input Majority Gate                               | 46       |

| 2.11. QCA Fork Inverter                                       | 47       |

| 3.1. Transformation Matrix of the Controlled-V Gate           | 55       |

| 3.2. Detailed QMDD Construction for the Controlled-V Gate     | 57       |

| 3.3. Local Complexity in a Trivial BDD Swap                   | 61       |

| 3.4. The General Case of Local Swap Affects the Cofactors     | 61       |

| 3.5. The Condition for a QMDD Skipped Variable                           | 63  |

|--------------------------------------------------------------------------|-----|

| 3.6. Transformation Matrix for a 2-variable Gate in a 3-variable Circuit | 65  |

| 3.7. QMDD with One and Two Skipped Variables                             | 68  |

| 3.8. The HCH Circuit                                                     | 69  |

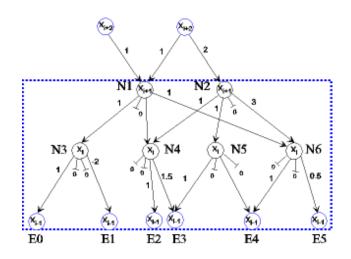

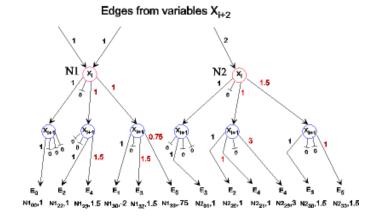

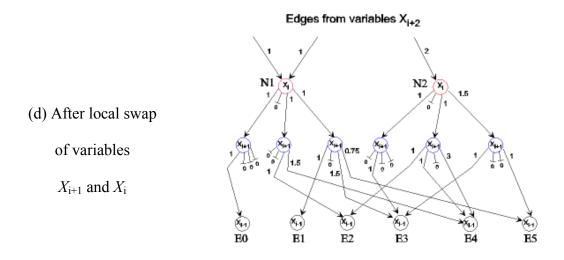

| 3.9. QMDD Local Variable Swap Example                                    | 74  |

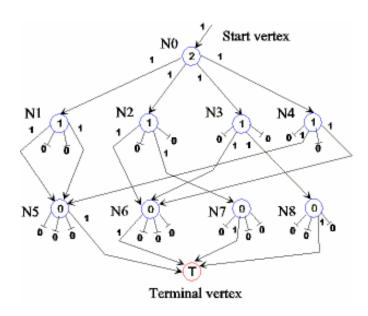

| 3.10. 3-variable Benchmark Circuit "c3_17"                               | 79  |

| 3.11. The QMDD for Benchmark Circuit "c3_17"                             | 80  |

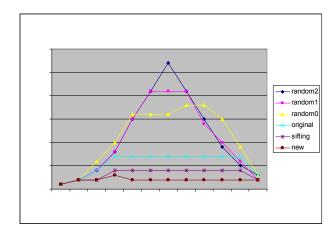

| 3.12. Benchmark Circuit "cycle10_2" Changes from FLAT to PEAR            | 88  |

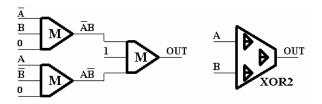

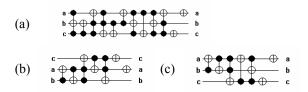

| 4.1. 2-input XOR Gate Implementation                                     | 93  |

| 4.2. 3-input XOR Gate Implementation                                     | 94  |

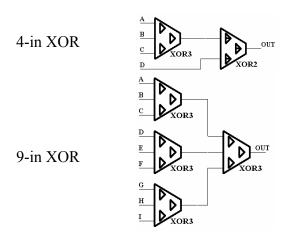

| 4.3. Implementation of multi-input XOR Gates                             | 95  |

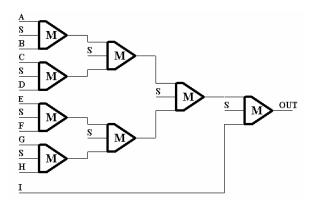

| 4.4. Implementation of a 9-input AND or OR Gates                         | 96  |

| 4.5. An Overview of the QCAexor Tool                                     | 97  |

| 4.6. VHDL Model of a Fredkin Gate                                        | 102 |

| 4.7. Place and Route Map of the 16-bit Brent-Kung PPA                    | 104 |

| 4.8. The RTL Viewer Output for the 8-bit Brent-Kung PPA                  | 104 |

| 4.9. The Size and Delay Comparison of Classical and Reversible PPAs      | 105 |

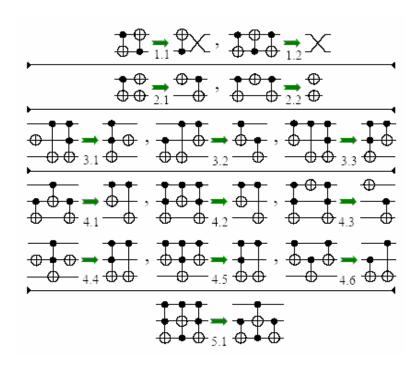

| 4.10. MMD's Templates for 2x2 and 3x3 Quantum Circuits                   | 109 |

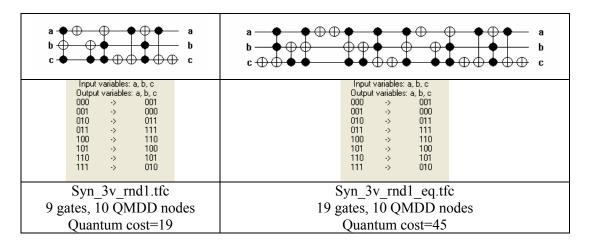

| 4.11. Functionally Equivalent Circuits of Different Sizes                | 117 |

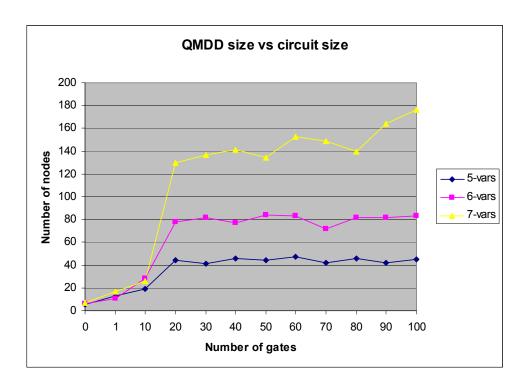

| 4.12. QMDD Size for the Circuits of Table 4.4.                           | 120 |

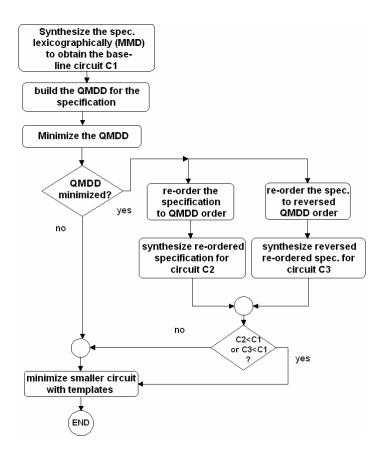

| 4.13. The "QMDDsyn" Framework                                            | 122 |

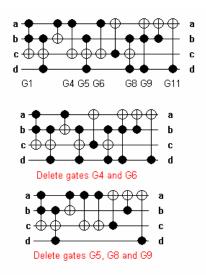

| 4.14 Minimization of the Circuit of Example 4.2                          | 124 |

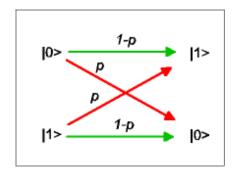

| 5.1. | The Binary Symmetry Channel Fault Model | 133 |

|------|-----------------------------------------|-----|

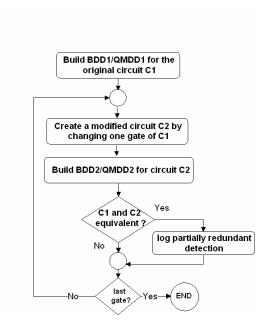

| 5.2. | Detection of Partially Redundant Logic  | 137 |

| 5.3. | Results with File "random4"             | 145 |

## LIST OF TABLES

# Table

| 2.1. | Single Qubit Operations                                        | 35  |

|------|----------------------------------------------------------------|-----|

| 3.1. | Experimental Results – Binary Circuits                         | 76  |

| 3.2. | Size Comparison between QMDD and QuIDDPro                      | 77  |

| 3.3. | Metric Values for Benchmark Circuit "3_17.nct"                 | 83  |

| 3.4. | Histograms for "hwb12" and "cycle10_2*"                        | 84  |

| 3.5. | Improvements in QMDD Minimization                              | 87  |

| 3.6. | Simulation of Implicit and Explicit QMDD Vector Multiplication | 90  |

| 4.1. | Comparison for ALU4.PLa - 14 inputs/8 outputs                  | 99  |

| 4.2. | Potential Gains in ESOP Synthesis for QCA                      | 100 |

| 4.3. | Maximal and Minimal QMDD' Size vs. Circuit Size                | 118 |

| 4.4. | Maximal and Minimal QMDD Size versus Circuit Size.             | 119 |

| 4.5. | Re-ordering the Specification for Example 4.2.                 | 123 |

| 4.6. | QMDDsyn Synthesis Results                                      | 126 |

| 5.1. | Gate Replacements for Irreversible Logic                       | 138 |

| 5.2. | Hidden Replacements in Irreversible Logic                      | 142 |

| 5.3. | No Hidden Replacements in Reversible Logic                     | 144 |

## **DEDICATION**

To my dear wife Orna Feinstein,

to my good friend Avery More, and

in memory of my father Benjamin Feinstein (1921-1986)

#### CHAPTER 1

#### INTRODUCTION

Quantum mechanics is the thought revolution of the 20<sup>th</sup> century. The Einstein, Podolsky, and Rosen experiment created a paradox when a pair of two entangled photons go in different directions and undergo polarization measurements. The pair seems to affect the polarization of each other while they are separated by a long distance [EPR35]. The EPR experiment suggested the possibility of hidden variables of quantum particles that inherently cannot be measured. The Heisenberg uncertainty principle further complicated the intuitive interpretation of the emerging quantum mechanics field [Heis30]. The Copenhagen interpretation during the 1930s, led by Niels Bohr, promoted the notion that a particle property may be considered real only when it is actually measured [Waer67, Omne99]. Bell's theorem proved that no hidden variable theory that preserves locality and determinisms can explain the prediction of quantum mechanics for an entangled photon pair [Bell64]. The field of quantum mechanics has seen tremendous developments since that time, but it is still entangled with magnificent wonders and phenomenon that defy our intuition.

Quantum mechanics was bridged to computing when Richard Feynman demonstrated in 1982 that various quantum mechanics effects cannot be simulated

properly on classical computers [Feyn82]. This observation brought forth the idea that perhaps we can obtain a new type of efficient computation if the computer itself is made to use quantum effects natively. Feynman and David Deutsch independently conceived the notion of the quantum computer in 1985 [Feyn85, Deut85]. Deutsch and Jozsa followed with the observation that quantum systems exhibit exponential increase in parallelism when the system size is increased [DJ92]. In 1993, Bennett et al. invented the notion of quantum teleportation [BBC+93]. A critical breakthrough was Peter Shor's seminal paper of 1994 that illustrated how a quantum computer may be able to factor primes exponentially faster than classical computation [Shor94]. Since the difficulty of factoring a large number into primes lies at the heart of the RSA encryption algorithm, such a potential breakthrough immediately caught worldwide attention. Lev Grover's search algorithm in 1996 that breaks the classical barrier of O(n) with an  $O(\sqrt{n})$  complexity further accelerated research interest in the new field of quantum computing [Grov96]. However, the prospects of better performance were not the only motivation for the immense interest we now see in quantum computing.

It has been projected that by 2018, mainstream CMOS technology will not be able to follow Moore's Law of speed and density doubling every 18 months [XCN+06]. So far, technologists have been able to overcome major hurdles such as lithographic limits, power constraints, electric field breakdown, and leakage currents. However, the accelerated shrinkage of circuit dimensions will eventually bring the size of basic circuit elements to the molecular and atomic scale where quantum phenomena rules prevail.

This is the boundary which spells the imminent demise of conventional CMOS technology and motivates us to investigate quantum technology.

Ray Kurzweil and other futurists noted that regardless of the hurdles, overall technology must continue to follow Moore's Law, causing new technologies to be invented [Kurz07]. And indeed, the projected demise of CMOS spawns the arrival of *quantum computing* (QC). We briefly describe the fundamentals of quantum computing in Chapter 2, where, in a somewhat simplistic approach, we include several technologies whose basic circuit elements must deal with individual atoms at the quantum phenomenon level.

#### 1.1. Emerging Quantum Computing Technologies

Emerging quantum nanotechnologies have been developed in the hope of achieving a performance that goes beyond the end-of-the-curve limits of CMOS.

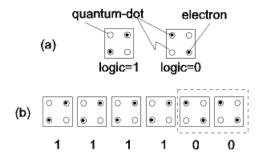

Quantum-dot cellular automata (QCA), invented by Lent et al. in 1993 [LTP93, TLP93], is a very promising technology. QCA had become the topic of intense research due to its projected size density of several orders of magnitude smaller than CMOS. It also promises fast switching time in the range of 10<sup>-12</sup> to 10<sup>-15</sup> seconds, and extremely low power. Experimental circuits utilizing metal dots were demonstrated in the late 90s [AOSL98], followed by the recent development of molecular QCA circuits [QSL+03].

QCA is radically different from today's CMOS technology. Information in QCA propagates along a line of cells via Coulombic charge interactions as opposed to conventional electric current as used in CMOS devices. Unlike the gate versatility of CMOS, the QCA technology natively implements the 3-input majority gate as the basic

building block. QCA also requires a new multi-zone clock mechanism for proper data propagation, prompting electrical and magnetic based solutions. The 3-input majority gate can easily implement 2-input AND or OR gates provided the third input is set at the logic '0' or '1' state, respectively. However, to avoid the waste of fixed logic states in one third of the inputs, researchers have been investigating improved utilization of all three inputs of the majority gates [ZWWJ04, WSJ+04]. QCA fundamentals are further described in Chapter 2.3.

In classical irreversible logic design, the circuit's inputs are evaluated to provide the output results in a process that does not preserve input information once the output is computed. As a result, one cannot recreate the inputs from the output information. In the extreme case of a decision circuit, an *n*-bit input is processed to obtain a single bit yes/no result. Clearly there is no way that a one bit result can re-construct an *n*-bit input. In contrast, reversible logic circuits have the main property that the circuit's input information can be fully reconstructed at any time from the output [NC00].

Landauer's principle states that each erasure of one bit of information dissipates at least  $K_BT$ ln2 energy, where  $K_B$  is the Boltzmann's constant and T is the temperature [L61]. Pioneering work by Bennet [Benn73], Fredkin and Toffoli [FT82], and Feynman [F85] illustrated the potential of reversible logic to create circuits with theoretical zero internal power dissipation. Reversible logic circuits are modeled as bijective functions that allow the full reconstruction of the circuit's input information from the output, thus eliminating the energy loss with the absence of erased bits. While Landauer's erasure energy is currently many orders of magnitude below today's CMOS

leakage current, it will play a major role in the future, posing a limiting factor for QCA and other futuristic *irreversible* logic circuits. As a result, the common consensus among computer scientists and theoretical physicists is that the long term quantum technology is likely to be based on reversible logic.

In addition to the theoretical elimination of energy loss, it seems that future implementation of quantum logic circuits based on optical or other quantum effects will necessarily be reversible for another reason - they impose the characteristic fan-in and fan-out of *one* due to the principle of conservation of matter.

We would like to emphasize that there are currently no substantial implementations of reversible QC circuits, although interesting small experimental circuits have been reported extensively [NC00, Hirv04]. An excellent recent survey of the architectural implementation of quantum computing technologies appears in [VMO06]. In contrast, logic reversibility can be synthesized and simulated on classical computers, as demonstrated in this research as well as in the large body of published relevant research [Cabe04].

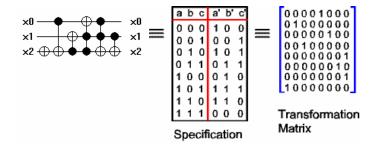

To fulfill the bijective relation between input and output, reversible logic circuits must have the same number of outputs as inputs (or have disallowed patterns on the largest set). To illustrate this initial discussion of reversible logic, Fig. 1.1 previews the Toffoli reversible logic gate that is commonly used for quantum computing and will be formally described in Section 2.2. Note that this gate has three inputs and three outputs, and the specification shows that every output set bijectively relates to a specific input set. The transformation matrix indicates the permutation relation between the 8

combinations of inputs  $(2^3)$  to the 8 combination of outputs  $(2^3)$ . For example, the first column indicates the mapping  $(a,b,c) \rightarrow (a',b',c')$ :  $000 \rightarrow 000$ , while the seventh column indicates the mapping  $110 \rightarrow 111$ . We will see in Chapters 2 and 3 that transformation matrices describing all quantum circuits are *unitary* and can consist of more complex mappings.

Figure 1.1. Transformation Matrix Representation of the Toffoli Gate

The requirement of a bijective relation between inputs and outputs can easily lead to a large number of unused (garbage) outputs for circuits with more inputs than outputs, and poses an immediate challenge for logic synthesis in order to minimize the garbage outputs. One can readily imagine the exponential explosion of the transformation matrix size with increasing numbers of lines.

Although general QC is materially different than QCA, we believe that there is some interesting commonality to allow their mutual inclusion in the present research. Both technologies are so radically different than CMOS that they require major new design paradigms to deal with circuit simulation, synthesis, and testing. The different

approaches taken with each technology provides added insight to the uniqueness of quantum computing.

#### 1.2. Quantum Computing Computer Aided Design Tools

Following the development of classical digital logic, emerging QC technologies rely heavily on *computer aided design* (CAD) tools. For this dissertation we have developed several CAD tools that encompass the main targets of synthesis, simulation, testing and verification. Fig. 1.2 provides an overview of the QC CAD tools.

Figure 1.2. Overview of the Quantum Computing CAD Tools

Several of our tools are based on the *quantum multi-valued decision diagram* (QMDD) originally proposed by Miller and Thornton to simulate and specify the transformation matrix of reversible logic circuits in a compact form [MT06, MTG06]. Like all decision diagrams, QMDD suffers from the exponential size explosion of the data structure so that size minimization becomes crucial. In this dissertation, we have

further developed the *QMDDsift* package that includes a sift-like minimization [MFT07, MFT07b]. Further minimization improvements were achieved with the *QMDDmet* tool that guides the minimization process based on the structure metrics [FTM08b]. We have used various implementations of the QMDD packages to simulate QC benchmark circuits, as well as simulation of vector multiplication [GTFM07].

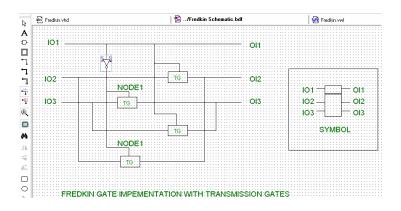

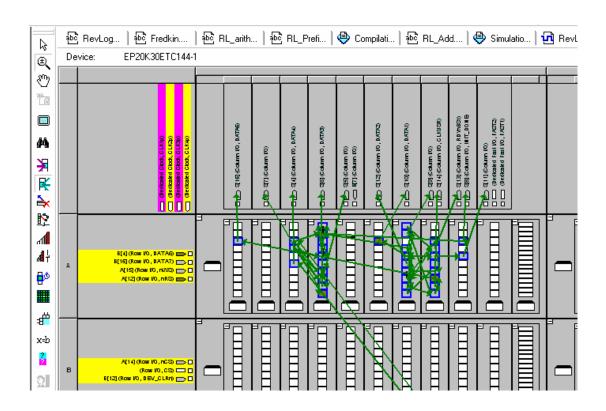

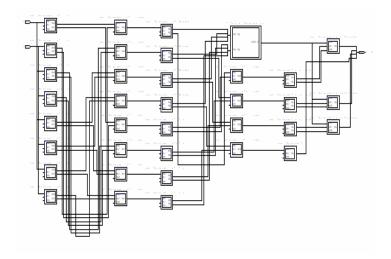

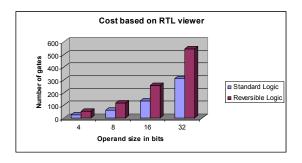

The *QCAexor* logic synthesis tool for QCA using *exclusive-OR sum of products* (ESOP) minimization is detailed in [FT07]. The major efforts in this dissertation target QC and classical reversible logic synthesis. In our initial work on reversible logic synthesis, we developed the *Virtual Fredkin Translation* tool [FTN07]. Using *Altera's Quartus II* common synthesis tool, we demonstrate how to virtually implement relatively complex logic circuits in reversible Fredkin gates. This approach, as discussed in Section 4.2, allowed us to gain a preliminary glimpse into the size and speed complexities of reversible logic. However, since this approach cannot control the exploding number of garbage outputs it is not intended as a replacement for other approaches to synthesize cascades of gates.

The state-of-the-art of gates cascade synthesis is currently limited to twenty inputs or less [AP05]. The *QMDDsyn* tool improves lexicographic synthesis of reversible logic by employing improved variable ordering as obtained by the QMDD package.

Quantum logic testing and verification is quite different from standard logic. It was shown by Agrawal that reversible logic circuits are easier to test since a single fault detection implies the ability for multiple fault detection [Agra81]. On the other hand,

testing of QC bring us to the problem of measurement in the quantum mechanics sense.

The QC decoherence problem (described in Chapter 2) mandates the extensive use of

QC fault tolerance techniques. There is also the unique issue of probabilistic testing

versus deterministic testing.

The QMDDceq tool is useful for both *design for test* (DFT) and verification. It investigates the detection of partially redundant reversible logic. We have also developed a similar tool (called *CMBtest*) for classical irreversible logic. Compared results between reversible and irreversible logic enable us to gain new theoretical insight into reversible logic.

#### 1.3. Impact and Contributions of this Research

We made several contributions to the major disciplines of CAD for QC, including simulation, synthesis, testing, and verification. In simulation, our work resulted in an improved QMDD package that can dynamically reduce its size and accommodate larger quantum circuits. Our work on data metrics based QMDD minimization represents a novel approach to *decision diagram* (DD) minimization, and may have application with other DD packages. We developed several approaches for reversible logic and for QC synthesis. We also introduce a new method to synthesize logic within the native 3-input majority gates of QCA. The QMDDceq tool for detecting partially redundant logic in reversible logic has ramifications for design verification, and for *design for test* (DFT) issues. Our comparative work on detection of partially redundant logic in irreversible logic can enhance traditional logic synthesis by eliminating wasted resources.

Our work on improving the QMDD and using it in various tools may prompt other researchers to further exploit the QMDD (or other DD tools for QC) for different CAD tasks beyond those explored in our research.

In addition to the experimental success of our various tools, several theoretical contributions have been made throughout this dissertation.

There is no doubt that the field of quantum computation is exploding. In fact, Adan Cabello's monumental bibliographic compendium on the foundation of quantum mechanics and quantum information details more than 11,000 publications [Cabe04]. This research further provides a contemporary survey of various theoretical and practical aspects of QC CAD. As we feel that QC logic synthesis is a crucial barrier in the development of QC, we made an effort to cover many different synthesis methods at some length, in addition to the disclosure of our original work. A good portion of the prior work we cite in this dissertation does not appear in the widely cited text book "Quantum Computation and Quantum Information" published by Nielsen and Chuang in 2000 [NC00]. We therefore hope that this dissertation will prove to be useful for other researchers who are new to this field.

#### 1.4. Organization

The remainder of this dissertation is organized as follows. In Chapter 2 we discuss the fundamentals of the transition from quantum mechanics to quantum computing. Chapter 3 is devoted to the representation and simulation of QC and classical reversible logic. It introduces the QMDD package and details our novel minimization techniques. Chapter 4 discloses our contributions for reversible logic

synthesis as well as the *QCAexor* QCA synthesis tool. Our work on QC testing and verification is presented in Chapter 5.

Chapter 2 covers the fundamentals background for this research. We briefly survey the key ideas of quantum mechanics from the Stern-Gerlach experiment to entanglement. We then discuss the important issues of *measurement* and *decoherence* in view of the 3<sup>rd</sup> postulate of quantum mechanics. We then expand on the basic properties of reversible logic. With this theoretical foundation we proceed to outline the basic ideas of QC and quantum information as they evolved from quantum mechanics. Special attention is spent on quantum operations and elementary quantum gates since these are the building blocks used in our research. We conclude this chapter with a discussion of the QCA fundamental properties.

We open Chapter 3 with a discussion of classical *binary decision diagrams* (BDD) followed by a survey of QC simulation on computers using various BDDs. The novel QMDD simulation package is introduced followed by a detailed discussion of the sift-like minimization tool *QMDDsift* [MFT07, MFT07b]. We then disclose our recent work on QMDD minimization based on QMDD data structure metrics [FTM08b]. We conclude Chapter 3 with our simulation results of QC benchmark circuits from the Maslov web-page [Masl05] and briefly discuss the simulation of vector matrix multiplication [GTFM07].

Chapter 4 is dedicated to the synthesis of quantum circuits, where we start with our work on ESOP transformation to majority gates for QCA [FT07] and virtual implementation of reversible logic [FTN07]. We follow with a brief but comprehensive

survey of current approaches for reversible and QC synthesis. We close with a detailed discussion of our contribution to lexicographical synthesis using variable selection based on the *QMDDsyn* tool variable order.

We turn our attention to QC testing and verification in Chapter 5. We start with a survey of reversible logic testing techniques and various proposals to create a unified QC fault model. Our contribution for QC verification is then disclosed with a detailed description of the *QMDDceq* tool.

Finally, our conclusions and future research areas appear in Chapter 6. In view of the nascent nature of QC, it should be no surprise that we foresee substantial future areas of work in all the aspects of quantum computing CAD outlined in this research.

#### **CHAPTER 2**

#### FROM QUANTUM MECHANICS TO QUANTUM COMPUTING

Quantum computing developed in the past two decades from the core ideas of quantum mechanics that shook the physics world in the 1930s. In this chapter we delve into some of the major concepts of quantum mechanics and show how they evolved into today's foundation of quantum computing and quantum information. Fundamental ideas of reversible logic and QC that are crucial for this dissertation are introduced. We conclude this chapter with an introduction of QCA.

#### 2.1. Key Ideas of Quantum Mechanics

We briefly discuss several key ideas that are crucial to better understand the evolution of quantum mechanics into the framework of quantum computing and quantum information in this section. Section 2.1.1 starts with some fundamental concepts of linear algebra. We then illustrate the famous Stern-Gerlach experiment that justifies the notion of qubits and superposition. Section 2.1.4 follows with the four postulates of quantum mechanics to illustrate the importance of the Hilbert space, the Hamiltonian operation, and measurements. The discussion of measurement in quantum mechanics is rather detailed in view of its importance for QC.

#### 2.1.1. Linear Algebra Preliminaries

We briefly introduce a few of the concepts of linear algebra that are crucial to understand quantum circuits. More extensive background is available in [NC00, MM05, Saku92, Bohm01, Holl90, Dira58, Lawd67].

We start with the famous Dirac notation for complex vectors, which use a clever play on the pseudo-word "braket".

**Definition 2.1:** (Dirac Notation). A complex vector u which is represented by a single column vector is called a *ket* vector and is denoted as  $|u\rangle$ . A complex vector v which is represented by a single row vector is called a bra vector and is denoted as  $\langle v|$ .

**Definition 2.2:** An inner product produces a complex number while operating on two vectors  $|u\rangle$  and  $|v\rangle$ . The vector space  $C^n$  has an inner product defined as

$$((u_1, u_2, u_3, ..., u_n), (v_1, v_2, v_3, ..., v_n)) = \sum_{i} u_i^* v_i$$

(2.1)

in Dirac notation, the inner product of  $|u\rangle$  and  $|v\rangle$  is denoted as  $\langle u|v\rangle$  where  $\langle u|$  is formed as  $|u^*\rangle^T$ .

**Definition 2.3:** A vector space  $C^n$  that includes the inner product operation is called *Hilbert* space. The Hilbert space is commonly denoted  $\mathcal{H}_n$ .

We can span the Hilbert space  $\mathcal{H}_n$  with the following  $\{|0\rangle, |1\rangle, ..., |i\rangle, ..., |n-1\rangle\}$  set of basis vectors. These kets are defined as

$$|0\rangle = \begin{bmatrix} 1\\0\\\vdots\\0 \end{bmatrix}, |1\rangle = \begin{bmatrix} 0\\1\\\vdots\\0 \end{bmatrix}, \dots, |i\rangle = \begin{bmatrix} 0\\\vdots\\1\\\vdots \end{bmatrix}, \dots, |n-1\rangle = \begin{bmatrix} 0\\0\\\vdots\\1 \end{bmatrix}$$

$$(2.2)$$

The same Hilbert space  $\mathcal{H}_n$  may be spanned by the  $\{\langle 0|,\langle 1|,...,\langle i|,...\langle n-1|\}\}$  set of bra basis vectors.

A complex state vector  $\psi$  in a Hilbert space  $\mathcal{H}_n$  is noted as

$$|\psi\rangle = \alpha_0 |0\rangle + \alpha_1 |1\rangle + ... + \alpha_i |i\rangle + ... + \alpha_{n-1} |n-1\rangle$$

(2.3)

where  $\alpha_0, \alpha_1, ... \alpha_i, ... \alpha_{n-1}$  are complex valued scalars. Each ket vector  $|\psi\rangle$  has a dual bra vector  $\langle \psi|$  which is defined as

$$\langle \psi | = \alpha_0^* \langle 0 | + \alpha_1^* \langle 1 | + \dots + \alpha_i^* \langle i | + \dots + \alpha_{n-1}^* \langle n-1 |$$

(2.4)

**Example 2.1:** The following example demonstrates the *inner* and *outer* products of qubit states using the Dirac notation. Let  $|\psi_1\rangle = (I, -i)^T$  and  $|\psi_2\rangle = (e^{-i}, -1)^T$ , then the inner product is

$\langle \psi_1 | \psi_2 \rangle = 1 \times e^{-i} + (-i) \times (-1) = e^{-i} + i$ , and the outer product is

$$|\psi_1\rangle\langle\psi_2|=\begin{pmatrix}1\\-i\end{pmatrix}(e^{-i},-1)=\begin{pmatrix}e^{-i}&-1\\-ie^{-i}&1\end{pmatrix}.$$

Let the linear operator  $\mathbf{A}^*$  be the complex conjugate of linear operator  $\mathbf{A}$ . For a linear operator A on a Hilbert space  $\mathcal{H}_n$  there exists a Hermitian conjugate or adjoint such that  $\mathbf{A}^+ = (\mathbf{A}^T)^*$ . The linear operator  $\mathbf{A}^+$  acts on space  $\mathbf{V}$  so that for all vectors  $|v\rangle$ ,  $|w\rangle \in \mathbf{V}$ , we have

$$(|\nu\rangle, A|w\rangle) = (A^+|\nu\rangle, |w\rangle). \tag{2.5}$$

**Definition 2.4:** A matrix U is said to be *unitary* if U<sup>+</sup>U=UU<sup>+</sup>=I. Thus, a unitary matrix or unitary operator is reversible by definition.

Unitary operators preserve inner products between vectors so that  $\langle x|y\rangle = \langle \mathbf{U}x|\mathbf{U}y\rangle$ . Their determinant is unity and they preserve the norms, that is  $||x|| = ||\mathbf{U}x||$ . The rank of a unitary matrix  $\mathbf{U}$  defined over  $C^n$  is n.

The importance of the unitary operation is illustrated in the second postulate of quantum mechanics which will be described in Section 2.1.3.

**Definition 2.5:** A  $k \times k$  unitary matrix **U** is called *special unitary* and marked  $\mathbf{U} \in \mathbf{SU}(k)$  if the determinant of **U** is equal to 1.

**Lemma 2.1:** Any special unitary 2×2 matrix U can be decomposed as follows:

$$\mathbf{U} = \begin{bmatrix} e^{i\alpha/2} & 0 \\ 0 & e^{-i\alpha/2} \end{bmatrix} \times \begin{bmatrix} \cos(\theta/2) & \sin(\theta/2) \\ -\sin(\theta/2) & \cos(\theta/2) \end{bmatrix} \times \begin{bmatrix} e^{i\beta/2} & 0 \\ 0 & e^{-i\beta/2} \end{bmatrix}$$

(2.6)

for real valued  $\theta$ ,  $\alpha$ , and  $\beta$ .

**Proof:** Since the rows and columns of a unitary matrix must be orthonormal, every 2×2 unitary matrix **U** can be written as

$$\begin{bmatrix} e^{i(\delta+\alpha/2+\beta/2)}\cos(\theta/2) & e^{i(\delta+\alpha/2-\beta/2)}\sin(\theta/2) \\ -e^{i(\delta-\alpha/2+\beta/2)}\sin(\theta/2) & e^{i(\delta-\alpha/2-\beta/2)}\cos(\theta/2) \end{bmatrix}$$

(2.7)

where  $\delta$  is also real valued. For a special unitary matrix, the determinant must be 1 so that  $e^{i\delta} = \pm 1$ . The factorization in (2.6) then follows.

**Definition 2.6:** The tensor product of  $r \times s$  and  $t \times u$  matrices, also called Kronecker product, is an  $rt \times su$  matrix defined by

$$\mathbf{A} \otimes \mathbf{B} = \begin{bmatrix} a_{11}\mathbf{B} & a_{12}\mathbf{B} & \dots & a_{1s}\mathbf{B} \\ a_{21}\mathbf{B} & \dots & a_{2s}\mathbf{B} \\ \vdots & \ddots & \vdots \\ a_{r1}\mathbf{B} & a_{r2}\mathbf{B} & \dots & a_{rs}\mathbf{B} \end{bmatrix}$$

$$(2.8)$$

### 2.1.2. The Stern-Gerlach Experiment and the Idea of Superposition

Figure 2.1. The Stern-Gerlach Experiment

The Stern-Gerlach experiment from 1922 posed one of the first paradoxes of quantum mechanics [SG22, Heis30]. The original experiment used an oven that heated silver atoms and the source particle beams were polarized using a magnetic field that operated on the particle spins. Later versions with hydrogen atoms as well as with polarized light conveyed the same paradoxical result. We assume that the source particle beams enter the first left Z polarizer of Fig. 2.1 and being polarized to components  $|+Z\rangle$  and  $|-Z\rangle$ . The  $|-Z\rangle$  beam is blocked and the  $|+Z\rangle$  beam is sent to the second polarizer, which operates along the X basis.

The  $|+Z\rangle$  is polarized again into two beams,  $|+X\rangle$  and  $|-X\rangle$ . The results after the second X polarizer are indeed quite intuitive. The paradox appears on the third Z polarizer which seems to recreate the  $|-Z\rangle$  by magic, since the  $|-Z\rangle$  beam was clearly blocked after the first polarizer.

**Definition 2.7:** We define the *qubit* (quantum bit) model as representing the general state of a single quantum bit  $|x\rangle$  with the vector:

$$|x\rangle = \alpha |0\rangle + \beta |1\rangle \tag{2.9}$$

where  $\alpha$  and  $\beta$  are complex numbers satisfying the relation:

$$|\alpha|^2 + |\beta|^2 = 1.$$

(2.10)

Extrapolating the notion of a qubit to the state of the beams in the Stern-Gerlach experiment, we can explain the paradox if we make the following assignments:

$$|0\rangle \rightarrow |+Z\rangle; |1\rangle \rightarrow |-Z\rangle; (|0\rangle + |1\rangle)/\sqrt{2} \rightarrow |+X\rangle; \text{ and } (|0\rangle - |1\rangle)/\sqrt{2} \rightarrow |-X\rangle.$$

(2.11)

We assume that the Z polarizer works on the basis  $\{|0\rangle, |1\rangle\}$  and the X polarizer works on the basis  $\{(|0\rangle+|1\rangle)/\sqrt{2}$ ,  $(|0\rangle-|1\rangle)/\sqrt{2}$ . If we further assume that the state of the beam after the first Z polarizer is  $|+Z\rangle=|0\rangle$  which equals to  $(|+X\rangle+|-X\rangle)/\sqrt{2}$ , it follows that the state after the second X polarizer includes a superposition of both  $|0\rangle$  and  $|1\rangle$ , hence the recreation of the  $|-Z\rangle=|1\rangle$  by the third polarizer.

#### 2.1.3. The Four Postulates of Quantum Mechanics

While quantum mechanics deals with very complex phenomenon and provides results that may be regarded as counterintuitive, it is very interesting that the following four relatively simple postulates quite successfully define the foundation of this field.

### Postulate 1 – The Hilbert Space of a Closed System S

A closed system S takes place in the quantum mechanics sense in a complex Hilbert space called the state space of S. As defined in Section 2.1.1, the Hilbert space is a complex vector space that includes the inner product. S is completely specified by the unit vector  $|\psi\rangle$ . Two states are equivalent *even* if they differ by a phase. Thus,  $|\psi\rangle$  is equivalent to  $|\psi'\rangle$  if, and only if,

$$|\psi'\rangle = e^{i\theta} |\psi\rangle \tag{2.12}$$

#### Postulate 2 – The Change of the State of a Closed Quantum System S

A closed quantum system changes in time along a unitary transformation U. The unitary operator U depends only on the times  $t_1$  and  $t_2$  to describe the time evolution

$$|\psi_{t_2}\rangle = \mathbf{U} |\psi_{t_1}\rangle. \tag{2.13}$$

Werner Heisenberg first formulated this relation in 1925. A few months later, M. Born and P. Jordan recognized the use of matrix algebra for this formulation [Wear67, Heis30]. Alternatively, we can describe the time evolution of the system *S* by the Schrödinger equation

$$i\hbar \frac{\partial}{\partial t} |\psi\rangle = \mathbf{H} |\psi\rangle \tag{2.14}$$

where  $\hbar$  is Planck's constant, and **H** is the fixed self-adjoint (Hamiltonian) operator of the system *S*. We note that a unitary operation is always reversible since the inverse of a unitary matrix is equivalent to its complex conjugate. Dirac and Von Neumann independently showed that equation 2.14 and 2.15 are equivalent [Vonn95, Dira58, Lawd67].

#### <u>Postulate 3 – Quantum Measurements</u>

Quantum measurements are described by a collection of measurement operators  $\{M_m\}$ . Each operator, called an observable, has the spectral decomposition

$$M_m = \sum_m m P_m \tag{2.15}$$

where  $P_m$  is the projector onto the eigenspace of eigenvalue m.

All the eigenvalues m of M describe possible results of the measurement. The probability of getting the result m while measuring  $|\psi\rangle$  is

$$p(m) = \langle \psi \mid M_m^+ M_m \mid \psi \rangle \tag{2.16}$$

This reduces  $|\psi\rangle$  to the post measurement state of  $|\psi'\rangle$

$$|\psi'\rangle = \frac{M_m |\psi\rangle}{\sqrt{\langle \psi | M_m^+ M_m |\psi\rangle}}$$

(2.17)

## Postulate 4 – Composite of Quantum States

The composite state space **H** of a group of states  $\{|\psi_1\rangle, |\psi_2\rangle, |\psi_3\rangle, ..., |\psi_n\rangle\}$  is the tensor product of these states. If the subsystems are in the states  $|\psi_i\rangle$ , then the joint state of the entire composite system is

$$|\Psi\rangle = |\psi_1\rangle \otimes |\psi_2\rangle \otimes |\psi_3\rangle \otimes ... \otimes |\psi_n\rangle \tag{2.18}$$

#### 2.1.4. Entanglement

A composite system  $|\Psi\rangle$  of the pair  $|x_i\rangle$  and  $|y_i\rangle$  can be represented as

$$|\Psi\rangle = \sum_{i} \sum_{j} \alpha_{ij} |x_i, y_j\rangle \text{ with } \sum_{i} \sum_{j} |\alpha_{ij}|^2 = 1$$

(2.19)

**Definition 2.8:** If the coefficients  $\alpha_{ij}$  in (2.16) can be written as  $\alpha_{ij} = \beta_i \gamma_j$ , the system is in a *decomposeable* state. Otherwise, the system is in an *entangled* state.

For example, the state  $\frac{1}{\sqrt{2}}(|00\rangle+|11\rangle)$  is entangled, while the state

$$\frac{1}{2}(|00\rangle+|01\rangle+|10\rangle+|11\rangle)$$

is decomposable.

The property of entanglement is crucial in many of the important algorithms that portray the major benefits of QC, including superdense coding and quantum teleportation [NC00, KLM07].

#### 2.1.5. Measurement and Decoherence in Quantum Mechanics

Measurement in quantum mechanics cause any state held at superposition to collapse to an observable result. Decoherence is the phenomenon by which a quantum state held at superposition tends to "decay" into the basis states, resulting in a loss of the quantum state information (similar to noise in classical computing and communication theory).

In the following discussion we show that the measurement of an observable of a quantum system comprised of a single qubit will always yield an eigenvalue of the Hermitian matrix A representing the measurement operator.

We first need to prove the following fundamental Theorem:

**Theorem 2.1:** The eigenvalues  $\lambda_i, \lambda_j, \ldots$  of a Hermitian operator **A** are real, and the eigenkets  $\zeta_i, \zeta_j, \ldots$  of **A** corresponding to different eigenvalues  $\lambda_i, \lambda_j, \ldots$  are orthogonal.

**Proof:** Following [Saku94], by definition of eigenvalues and eigenvectors

$$\mathbf{A} \mid \zeta_i \rangle = \lambda_i \mid \zeta_i \rangle \tag{2.20}$$

and because of the Hermitian properties,

$$\langle \zeta_j \mid \mathbf{A} = \lambda_j^* \langle \zeta_j \mid \tag{2.21}$$

By left multiplication of both sides of equation (2.14) by  $\langle \zeta_j |$ , right multiplication of both sides of equation (2) by  $|\zeta_j\rangle$ , and subtracting the two results, we get

$$(\lambda_i - \lambda_i^*) \langle \zeta_i | \zeta_i \rangle = 0 \tag{2.22}$$

First, let us assume that  $\lambda_j$ ,  $\lambda_i$  are the same eigenvalue. Since  $|\zeta_i\rangle$  is not the null ket, we must have  $\lambda_j = \lambda_j^*$ , which means that the **eigenvalues are real**.

If the eigenvalues are different, then since they are real, the first multiplicand of (2.22) cannot disappear. Thus we obtain the **orthogonality property**

$$\langle \zeta_i | \zeta_i \rangle = 0, \quad (\zeta_i \neq \zeta_i)$$

(2.23)

This completes the proof.

Before the measurement of the observable **A**, we can represent our system  $|\psi\rangle$  (not necessarily just the single qubit of the question) by the following linear combination:

$$|\psi\rangle = \sum_{\lambda} c_{\lambda} |\lambda\rangle \tag{2.24}$$

We now multiply on the left with  $\langle \lambda |$  and by applying the orthogonality property from theorem 2.1, we find that for all  $\lambda$ ,

$$c_{\lambda} = \langle \lambda \, | \, \psi \rangle \tag{2.25}$$

and consequently, equation (2.17) becomes

$$|\psi\rangle = \sum_{\lambda} |\lambda\rangle\langle\lambda|\psi\rangle \tag{2.26}$$

When the measurement is performed, the system is "thrown to" one of the eigenstates of the observable A, say  $|\lambda\rangle$ . This is what Dirac meant in his 1958 book regarding the postulate that "a measurement always causes the system to jump into an eigenstate of the dynamical variable that is being measured." In this sense, the result of the measurement yields one of the eigenvalues of the observable being measured. Since the observables are the quantum analogue of dynamical variables (e.g. position, spin, linear and angular momentum, energy, polarization), the theorem stating that the eigenvalues of the Hermitian operator **are real** is crucial. In other words, we cannot observe "complex" outcomes of measurements.

We note, of course, that if  $|\psi\rangle$  is already in the state  $|\lambda\rangle$ , the measurement by **A** yields the result  $\lambda$  with certainty.

However, postulate 3 of quantum mechanics states that the probability of the system being thrown to or collapsed to a particular eigenstate  $|\lambda\rangle$  is

$$P_{\lambda} = \left| \langle \lambda \, | \, \psi \rangle \right|^2 \tag{2.27}$$

This postulate insures us that the probability conforms to the requirements that each eigenvalue of **A** has a nonnegative probability. It also provides

$$\sum_{\lambda} P_{\lambda} = 1 \tag{2.28}$$

Since we deal here with a single qubit, the Hermitian observable **A** has two eigenvalues,  $\lambda_1$  and  $\lambda_2$  each with a probability as shown in (2.24). It should be noted that it is possible to have the original qubit already prepared in the eigenstate  $|\zeta_1\rangle$ . In this

case, the same observable **A** will result in the eigenvalue  $\lambda_1$  with certainty. This is similar to the case of measurements in repeated tests [MM05].

The measurement problem is one the key concepts of quantum mechanics. An interesting discussion relates to the famous Schrödinger's Cat Paradox [Schr35]. The single quantum bit has the basis states of ALIVE and DEAD, and while the cat is in the box, its state  $|\psi\rangle$  is the superposition of

$$|\psi\rangle = \alpha_1 |ALIVE\rangle + \alpha_2 |DEAD\rangle$$

(2.29)

A common superposition with 50/50 chance for the cat being alive is

$$|\psi_0\rangle = \frac{1}{\sqrt{2}}(|ALIVE\rangle + |DEAD\rangle)$$

(2.30)

The measurement observable  $\mathbf{A}$  of this qubit is performed by simply opening the box in which the "superpositioned" cat is enclosed. When the box is opened and a measurement is made, the system is "thrown to" (or collapses to) only one of the eigenvalues of the observable  $\mathbf{A} - ALIVE$  or DEAD. Clearly, the observable  $\mathbf{A}$  has the form

$$\mathbf{A} = \begin{pmatrix} ALIVE & 0 \\ 0 & DEAD \end{pmatrix} \quad \text{or} \quad \mathbf{A} = \begin{pmatrix} DEAD & 0 \\ 0 & ALIVE \end{pmatrix}$$

(2.31)

This observable was the basis of a huge debate at the heart of quantum physics: "What mechanism converts the probabilities of live/dead into such a sharp outcome?"

Briefly, there were the *Copenhagen Interpretation* (QC deals only with the probabilities of the observable quantities – all other quantities are just meta-physical), the *Quantum Decoherence* (the macroscopic nature of the measurement apparatus

allows physicists to distinguish the fuzzy boundary between quantum world and actual world) and other philosophies (non-scientific like "conscious collapse" etc.) [Bohm01, BCS04, Hirv04, MM05, Omne99].

A very detailed and modern discussion of the measurement problem and decoherence appears in Schlosshauer [Schl05]. Another extensive discussion appears in Chapter 3 of the original class notes from 1997 of John Preskill of Caltech [Pres97].

### 2.2. Reversible Logic

Quantum computation is reversible in nature. In this section we present the foundation of reversible logic. We show how reversible logic can be regarded from the point of view of group symmetry. Efficient reversible circuits that minimize garbage inputs and outputs are built in the form of cascades of gates that are defined in Section 2.2.3. We also discuss simple implementations of common logic functions that may be obtained directly from Toffoli and Fredkin gates.

## 2.2.1. Defining Reversible Logic

**Definition 2.9:** A gate or a circuit is logically *reversible* if it maps each input pattern to a unique output pattern. For classical reversible logic, the mapping is a permutation matrix. For quantum circuits, the gate or circuit operation can be described by a unitary transformation matrix. Another way to describe the notion of logically reversible circuits is to note that the functions describing the behavior of the circuits are bijective.

Reversible gates or circuits can be designed with a different number of inputs and outputs [Alra04b]. In such cases, not all the patterns of the largest set of outputs or inputs are used. However, in the main research stream and in the remainder of this dissertation we are concerned only with  $n \times n$  reversible circuits with equal number (n) of inputs and outputs. We should note inputs/outputs of reversible circuits are commonly referred to as "variables" or "lines" in this dissertation and in the literature [MM05, NC00].

Bennett showed that reversible gates can theoretically result in binary circuits that are completely free from energy loss [Benn73]. The concept of reversibility has been extended to *multiple-valued logic* (MVL) circuits [MDM04, Alra04b]. Binary quantum logic gates and circuits are inherently both logically and physically reversible [NC00]. Non-binary quantum logic circuits are logically reversible.

A variety of basic reversible gates have been proposed in the past few decades. In Chapter 1 we illustrated a 3-variable Toffoli gate in Fig. 1.1. We can easily extend the 3-variable Toffoli gate to an arbitrary n-variable Toffoli gate as shown in Fig. 2.2. It has n-1 control lines (filled circles) and one target line (open circle). For each gate, the value on the target line is negated if, and only if, all the n-1 control lines are set at '1'. We denote a n-variable Toffoli gate as  $TOF(x_0,x_1,...,x_{i-1},x_{i+1},...,x_{n-1};x_i)$ , where the target line  $x_i$  is separated by a semicolon from the control lines.

Figure 2.2. n-variable Toffoli Gate

A common alternate notation for this gate is [t,C] where t is the target line and C comprises the set of control lines. With this notation, the gate of Fig. 2.2 is denoted  $[x_i, \{x_0,x_1,...,x_{i-1},x_{i+1},...,x_{n-1}\}].$

A library of universal gates is a set of gates that can implement any arbitrary quantum circuit. We encounter classical reversible libraries like the NCT (not, control not, Toffoli), NCTF (NCT with Fredkin gate) and NCTFS (NCTF with the swap gate).

### 2.2.2. Symmetry in Reversible Logic

Let  $\rho: B^n \to B^n$  be a binary logic circuit with n inputs and outputs, where  $B = \{0, 1\}$ .

If  $\langle X_l, ..., X_n \rangle \in B^n$  and  $\langle Y_l, ..., Y_n \rangle \in B^n$  be the input and output vectors respectively, then there are  $2^n$  different assignments for the input vectors. A binary logic circuit  $\rho$  is reversible if, and only if, it is a one-to-one and onto function. Such a function is called a bijective function.

A binary reversible logic circuit with n inputs and n outputs is also called an nqubit binary reversible gate. There are a total of  $(2^n)!$  different n-qubit binary reversible circuits.

A bijective mapping s:  $M \rightarrow M$  can be written as

$$s = \begin{pmatrix} x_1, x_2, x_3, ..., x_n \\ x_{s1}, x_{s2}, x_{s3}, ..., x_{sn} \end{pmatrix}$$

(2.32)

and is called a permutation.

Figure 2.3. Toffoli Gate as a cycle(6,7) Operation

All the possible permutations form a group under the composition of mappings and is denoted by  $S_k$  [GFX06]. In Fig. 2.3 we demonstrate how the Toffoli  $T(x_0,x_1;x_2)$  gate is equivalent to cycle(6,7) operation when considered as a permutation.

#### 2.2.3. Reversible Gates Cascade

Reversible circuits are synthesized in the form of a cascade of gates. Fig. 2.4 shows the benchmark circuit "hbw5" which is the 5-variable hidden weighted bit function from the Maslov web page [Masl05]. The circuit uses 5 lines that represent 5 inputs and 5 outputs. Each vertical line depicts a controlled NOT gate (if the gate operates on only two lines) or generalized *n*-input Toffoli gates.

Figure 2.4. The 5-variable "hwb5" Cascade of Gates

This cascade example includes 54 gates illustrating the inherent complexity of quantum circuits. The transformation matrix of the entire circuit is computed by repeated matrix multiplication of the individual gates and the tensor product among the individual lines which results in an overall circuit transfer matrix of dimension  $32\times32$   $(2^5\times2^5)$ .

**Definition 2.10:** An *n*-variable reversible gate cascade is composed of adjacent reversible gates that operate on the same *n* variables represented by horizontal lines across the circuit. Each gate may be connected to one or more of the lines and must be extended via tensor product to affect all *n* lines.

Cascading of two reversible gates is equivalent to the multiplication of the two permutation matrices representing the corresponding gates. We demonstrate the computation of the transformation matrix on the smaller cascade of four gates shown in Fig. 2.5.

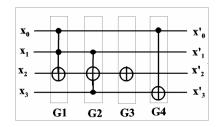

Figure 2.5. A Cascade of 4 Gates with 4 Variables

Each gate is part of a stage of the cascade which must include the gate and all the unconnected lines running through it. For example, gate G3, is a reversible NOT gate with a 2×2 transformation matrix. However, in view of the 4 variables that the circuit depends upon, it must have a  $16\times16$  transformation matrix. We thus extend the reversible NOT operation on variable  $x_2$  into a  $16\times16$  transformation matrix using the tensor product with the  $2\times2$  identity matrix  $\mathbf{I}_2$

$$G4 = \mathbf{I}_2 \otimes \mathbf{I}_2 \otimes \mathbf{NOT} \otimes \mathbf{I}_2 \tag{2.33}$$

The overall transformation matrix **C** of this cascade is obtained by multiplying the transformation matrices of the 4 gates in reverse order [MM05, NC00]. Thus,

$$\mathbf{C} = G4 \times G3 \times G2 \times G1 \tag{2.34}$$

#### 2.2.4. Logic Function Realization with Classical Reversible Gates

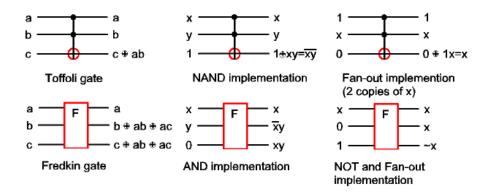

Many more classical reversible gates have been introduced including the Feynman (Control NOT), the Fredkin gate and the swap gate [FT82]. We will re-visit these gates as well as quantum reversible gates in the next Section. The Fredkin gate is defined in Fig. 2.6. Using only Toffoli and Fredkin gates, we show in Fig. 2.3 the

implementation of common classical logic operations (NAND, AND, NOT, and fan-out duplication). It is clear that once the NAND gate or the equivalent set of AND and NOT gates are achievable, any arbitrary logic function can be implemented. Note that these implementations require the extra cost of auxiliary inputs (also called ancilla inputs), which are crucial to the operation of the gates. For example, the Fredkin NOT and Fan-out implementation uses only one input for the input variable x, while the remaining gate inputs become ancillary inputs, initialized to either 0 or 1.

Figure 2.6. Logic Functions by Toffoli and Fredkin Gates

Since the number of outputs for reversible logic gates must equal the number of inputs, we find that reversible circuits can create a large number of unused or "garbage" outputs. Therefore, a major constraint in the synthesis, specification, and simulation of quantum circuits is the need to minimize the garbage outputs and the ancillary inputs.

#### 2.3. Quantum Computation and Quantum Information

The pioneering works of Feynman, Deutsch, Sozja, Shor, and Grover have spawned an immense interest in quantum computation and quantum information [RP00]. In Section 2.3.1 we briefly discuss their work to justify our interest in QC. We then describe the building blocks of quantum computation, starting with quantum bits (qubits) and quantum registers, and following with the basic quantum operations and gates. We conclude this section with the important Beck-Zeilinger-Bernstein-Bertani decomposition Theorem.

### 2.3.1. Quantum Computing Algorithms

The promise of QC was staked on the success of four important algorithms: dense coding, quantum teleportation, quantum prime factoring, and quantum search. The first two algorithms depend on the entanglement phenomenon. Quantum prime factoring and quantum search depends on the ultimate parallelism due to the superposition phenomenon. Both phenomena have no counterparts in classical computing.

In dense coding, a quantum communication channel allows for sending exponentially more information using entangled qubits rather than classical bits. For example, one entangled qubit has the information content of two classical bits [KLM07].

The important *no-cloning theorem* states that an unknown quantum state cannot be copied [NC00]. Bennett et al. discovered that quantum teleportation enables the

transmission of quantum states from point A to point B, using entangled pairs of qubits [BBC+93]. However, the original quantum state is destroyed in the process, thus complying with the no-cloning theorem.

Peter Shor's prime factorization uses repeated reduction of the factoring problem into an order finding problem and phase estimation problem. The solution for the later problem is based on the *quantum fast Fourier transform* (QFFT) and illustrates the inherent parallelism of QC [Shor94]. The Deutsch and Sozja algorithm also relates to QFFT [DJ92].

The quantum search algorithm is also based on exploiting the parallelism of superposition and was proposed by Grover [Grov96]. A quantum register with the search data is initialized and then transformed into a superposition by the Walsh-Hadamard transform (see Section 2.3.5). A repeated Grover's iteration step which utilizes a special oracle is performed to "amplify" the searched items. This algorithm breaks the classical barrier of time complexity from O(n) to  $O(\sqrt{n})$  when searching a dataset of n items.

An important group of algorithms deals with simulating quantum systems as suggested by Feynman [Feyn85]. Ultimately, a future quantum computer will be the best choice for simulation of quantum systems. In the meantime, results such as our contribution in simulation (Chapter 3) illustrate the potentials and pitfalls when using classical computers to simulate quantum systems.

#### 2.3.2. Quantum Bits and Registers

The basic computing element in quantum computing is the *qubit*— the quantum bit that was defined in section 2.1.2. A qubit exists in a Hilbert space  $\mathcal{H}_2$  where it represents the superimposed state of the smallest unit of computational data. The simplest basis states that span  $\mathcal{H}_2$  are

$$|0\rangle = \begin{bmatrix} 1\\0 \end{bmatrix}$$

and  $|1\rangle = \begin{bmatrix} 0\\1 \end{bmatrix}$  (2.35)

Equation (2.7) showed that the qubit quantum state in the basis  $\{|0\rangle, |1\rangle\}$  can be described as  $|x\rangle = \alpha |0\rangle + \beta |1\rangle$ , where  $\alpha$  and  $\beta$  are complex numbers satisfying the relation  $|\alpha|^2 + |\beta|^2 = 1$ .

Before we measure the qubit state, it still represents a superposition of  $|0\rangle$  and  $|1\rangle$ . Once we actually measure the quantum state, we obtain the state  $|0\rangle$  with a probability of  $|\alpha|^2$  and state  $|1\rangle$  with probability  $|\beta|^2$ . Clearly, this superposition and the dependence on measurement is significantly different than the familiar classical computing where determinism ensures that '1' is a '1' and '0' is '0'.

A system of two qubits comprises a four-dimensional Hilbert space  $\mathcal{H}_4$  with the standard basis set of  $\{|00\rangle, |01\rangle, |10\rangle, |11\rangle\}$ . Obviously, other orthonormal basis sets can be used. This system is a *quantum register of two qubits*. Larger *quantum registers* are composed using the tensor product according to the 4<sup>th</sup> postulate of quantum mechanics (2.18). The superposition of the entire basis set in a quantum register is the source for

the parallelism potential of QC. There is no parallel for this phenomenon in classical logic.

# 2.3.3. Quantum Operations on a Single Qubit

The quantum operation on a qubit must be reversible and preserve the norm and the inner product. Therefore they are represented by  $2\times2$  unitary matrices. Although there is an infinite number of  $2\times2$  unitary matrices, we list some important single qubit operations in Table 2.1.

Table 2.1. Single Qubit Operations

| Name                                      | Unitary<br>matrix                                                                                                              | Symbol            | Name                                          | Unitary<br>matrix                                                                                                                | Symbol                         |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Pauli $\sigma_0 \equiv I$                 | $\begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix}$                                                                                 | <u> </u>          | Pauli $\sigma_1 \equiv \sigma_x \equiv X$ NOT | $\begin{pmatrix} 0 & 1 \\ 1 & 0 \end{pmatrix}$                                                                                   | <u>x</u>                       |

| Pauli $\sigma_2 \equiv \sigma_y \equiv Y$ | $\begin{pmatrix} 0 & -i \\ i & 0 \end{pmatrix}$                                                                                | Y                 | Pauli $\sigma_3 \equiv \sigma_z \equiv Z$     | $\begin{pmatrix} 1 & 0 \\ 0 & -1 \end{pmatrix}$                                                                                  | z                              |

| Hadamard                                  | $\frac{1}{\sqrt{2}} \begin{pmatrix} 1 & 1 \\ 1 & -1 \end{pmatrix}$                                                             | —[H]—             | Phase                                         | $\begin{pmatrix} 1 & 0 \\ 0 & i \end{pmatrix}$                                                                                   | <u> </u>                       |

| π/8                                       | $\begin{pmatrix} 1 & 0 \\ 0 & e^{i\pi/4} \end{pmatrix}$                                                                        | T                 | $R_{_{x}}(\theta)$                            | $ \begin{pmatrix} \cos\frac{\theta}{2} & -i\sin\frac{\theta}{2} \\ -i\sin\frac{\theta}{2} & \cos\frac{\theta}{2} \end{pmatrix} $ | $-\mathbf{R}_{x}$              |

| $R_{y}(\theta)$                           | $ \begin{pmatrix} \cos\frac{\theta}{2} & -i\sin\frac{\theta}{2} \\ \sin\frac{\theta}{2} & \cos\frac{\theta}{2} \end{pmatrix} $ | $-\mathbf{R}_{y}$ | $R_z(\theta)$                                 | $\begin{pmatrix} e^{-i\theta/2} & 0 \\ 0 & e^{i\theta/2} \end{pmatrix}$                                                          | $ \mathbf{R}_{\mathbf{z}}$ $-$ |

| V<br>Square root<br>of NOT                | $\frac{1+i}{2} \begin{pmatrix} 1 & -i \\ -i & 1 \end{pmatrix}$                                                                 | v                 | $\mathbf{V}^+ = \mathbf{V}^{-1}$              | $\frac{1-i}{2} \begin{pmatrix} 1 & -i \\ -i & 1 \end{pmatrix}$                                                                   |                                |

### 2.3.4. Elementary Quantum Gates and Quantum Circuits

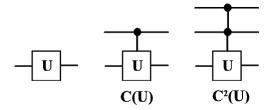

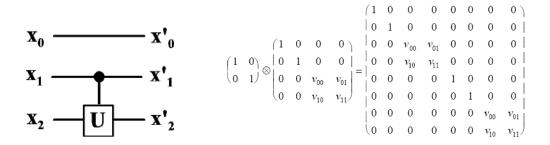

Feynman proposed the general notation for a controlled operation shown in Fig. 2.7 as an extension of a qubit operation that works on more than one variable [Feyn85]. This is similar to the n-variable Toffoli gates we have shown in Fig. 2.2, except that we use any general single qubit operation specified by the  $2\times 2$  unitary matrix, U, instead of the NOT operation used in classical reversible logic. Again, the control lines with dots are transferred without a change. The lower target line performs the unitary operation U only when all the control lines are set to  $|1\rangle$ . There is no limit on the number of control lines.

Figure 2.7. The General Controlled Operation

An alternate notation for the control operation is  $\wedge_{n-1}(\mathbf{U})$  as used in the seminal paper on elementary quantum gates by Barenco et al. [BBC+95]. Unlike the *n*-variable Toffoli gate shown in Fig. 2.2, the  $\wedge_{n-1}(\mathbf{U})$  notation is always normalized so that the control lines precede the target line. The transformation matrix for an *n*-variable  $\wedge_{n-1}(U)$  is the  $2^n \times 2^n$  matrix

$$\wedge_{n}(U) = \begin{pmatrix}

1 & & & & & \\

& 1 & & & & \\

& & 1 & & & \\

& & & 1 & & \\

& & & & 1 & & \\

& & & & 1 & & \\

& & & & u_{00} & u_{01} \\

& & & & u_{10} & u_{11}

\end{pmatrix} \tag{2.36}$$

Where the single qubit operation **U** is  $\begin{bmatrix} u_{00} & u_{01} \\ u_{10} & u_{11} \end{bmatrix}$ .

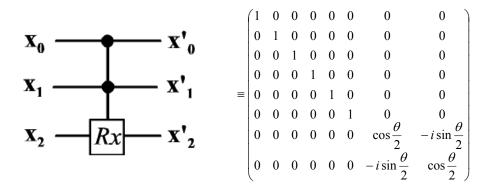

A variety of basic reversible gates that are realizable using quantum devices include the Deutsch-Toffoli, Controlled-NOT, Controlled-V, and controlled  $V^+$  and many more [KSV02]. Fig. 2.8 illustrates the Deutsch-Toffoli gate  $\wedge_2(R_x)$  which was shown to be a universal gate for quantum computing [Deut89]. We note that many other sets of quantum universal gate sets have been proposed.

Figure 2.8. The Deutsch-Toffoli Universal Gate

The Deutsch-Toffoli gate is a two-level unitary matrix. The two-level unitary matrix is formally defined as follows.

**Definition 2.11:** A two-level unitary matrix transforms only two or fewer vector components. Therefore, a  $n \times n$  two-level unitary matrix V that implements the unitary operation  $\mathbf{U} = \begin{bmatrix} u_{00} & u_{01} \\ u_{10} & u_{11} \end{bmatrix}$  is an identity matrix  $\mathbf{I}_n$  with two or fewer diagonal '1's

replaced by the unitary components of U. For example, equation (2.38) is an  $8\times8$  two-level unitary matrix, while a  $4\times4$  two-level unitary matrix V, may appear as

$$\mathbf{V} = \begin{bmatrix} u_{00} & 0 & u_{01} & 0 \\ 0 & 1 & 0 & 0 \\ u_{10} & 0 & u_{11} & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

(2.37)

Quantum circuits are represented as gate cascades and are of a form in a similar way to Figure 2.5 where the large variety of single qubit operations can replace the Toffoli NOT operator. We should note that a quantum gate cascade is actually a quantum register with control and time flowing from left to right [Cybe01]. It is for this reason that the overall circuit transformation matrix is formed as a product of gate component transformation matrices from right to left.

When synthesizing quantum and classical reversible circuits, it is often convenience to have a standardized cost measure that can help in the comparison of competing implementations. The following definition of the quantum cost of a circuit is used throughout this dissertation [Masl03]

**Definition 2.12:** The quantum cost of a circuit C is the number of elementary quantum operations that are required to implement the function of C.